PLL

Dvoukanálový GENERÁTOR harmonického signálu na principu DDS, 40 MHz (moje bakalářská práce)

www.elweb.cz

Integrovaný obvod AD9958 firmy Analog Devices (2) obsahuje dvě jádra DDS, která umožňují nezávislé nastavení frekvence, fázového posuvu a amplitudy pro oba kanály. Řídící obvody obou kanálů jsou taktovány shodným zdrojem hodinové frekvence a jsou tedy vzájemně synchronní. Právě proto je AD9958 vhodný pro tuto aplikaci.

www.elweb.cz

2.3.1. Vlastnosti

- 2 synchronní DDS jádra

- nezávislé nastavení frekvence, fáze a amplitudy obou kanálů

- přizpůsobené zpoždění změn parametrů výstupních signálů

- lineární rozmítání frekvence, fáze i amplitudy

- až šestnácti-úrovňová diskrétní modulace frekvence, fáze i amplitudy

- sériové řízení po SPI sběrnici

- dvojité napájecí napětí 1,8 V a 3,3 V

- možnost synchronizace více integrovaných obvodů

- integrovaná násobička vstupní hodinové frekvence (4x až 20x)

www.elweb.cz

- pouzdro 56-Lead LFCSP

V následující tab. 2.1 jsou uvedeny počty bitů jednotlivých částí integrovaného obvodu AD9958.

www.elweb.cz

Tab. 2.1 : Počty bitů částí AD9958

|

|

počet bitů |

|

výstupní D/A převodníky |

10 |

|

nastavení frekvence |

32 |

|

nastavení fáze |

14 |

|

nastavení amplitudy |

10 |

www.elweb.cz

2.3.2. Blokové schéma

Na obr. 2.1 je uvedeno vnitřní blokové schéma integrovaného obvodu AD9958 převzaté z (2). Jsou zde vidět obě jádra přímé digitální syntézy (DDS Core), řízení výstupní amplitudy (AMP), integrované digitálně-analogové převodníky (DAC) a řídící logika (Timing and control logic). Dále se v AD9958 nachází obvody pro generování a úpravu hodinového signálu včetně násobičky frekvence (REF clock multiplier) a obvody pro sériovou komunikaci.

www.elweb.cz

Obr. 2.1 : Blokové schéma AD9958

2.3.3. Vybrané parametry

www.elweb.cz

|

parametr |

hodnota |

|

Maximální hodinová frekvence |

500 MHz |

|

Maximální výstupní proud D/A převodníků |

10 mA |

|

Maximální chyba zesílení |

±10 % |

|

Maximální nelinearita |

±1 LSB |

|

Oddělení kanálů |

72 dB |

www.elweb.cz

www.elweb.cz

Následující obrázek obr. 2.2 zobrazuje blokové schéma celého přístroje tak, jak jsem jej navrhl. Přístroj jsem rozdělil na dvě samostatné části – digitální (horní část blokového schématu) a analogovou (spodní část). Tyto dvě části bude možno navrhovat, sestavovat a testovat samostatně, což zjednoduší celkovou realizaci. Digitální část slouží k řízení integrovaného obvodu AD9958 a také pro komunikaci s uživatelem. Tato část je tvořena mikrokontrolérem, ke kterému je připojen textový LCD displej 2x 16 znaků, Bluetooth modul pro bezdrátové ovládání a také maticová numerická klávesnice se šestnácti tlačítky pro ovládání přístroje.

Obr. 2.2 : Blokové schéma

www.elweb.cz

Analogovou část tvoří především integrovaný obvod přímé digitální syntézy AD9958. Jeho hodinová frekvence je vytvářena externím generátorem. Vstupy modulace jsou opatřeny vstupními přepěťovými ochranami a vstupními zesilovači. Výstupy AD9958 jsou komplementární a vysoko-impedanční. Pro jejich impedanční přizpůsobení na 50 Ω a změnu na jednoduché (nesymetrické) výstupy jsou použity diferenciální zesilovače. Za nimi pak následují rekonstrukční pasivní LC filtry typu dolní propust. Tyto filtry jsou rovněž impedančně přizpůsobeny na 50 Ω. Nakonec je signál napěťově i proudově zesílen výstupními zesilovači a opět přizpůsoben výstupními odpory opět na 50 Ω.

Jednotlivé části blokového schématu budou podrobněji popsány dále.

Celkové schéma přístroje je uvedeno v příloze.

www.elweb.cz

2.5.1. DDS

2.5.1.1. Zapojení AD9958

Integrovaný obvod AD9958 má 56, respektive s chladící ploškou 57 vývodů. Většina z nich je využita pro připojení napájecího napětí nebo zem. Následující tab. 2.2 je převzata z (2) a zobrazuje popis všech pinů. Po prostudování jednotlivých částí katalogového listu jsem ji doplnil o konkrétní využití (zapojení) jednotlivých pinů v této aplikaci.

Tab. 2.2 : Popis funkce a zapojení pinů AD9958

|

číslo pinu |

název pinu |

I/O |

popis funkce pinu |

zapojení |

|

1 |

SYNC_IN |

I |

Synchronizace více obvodů AD9958 |

GND |

|

2 |

SYNC_OUT |

O |

Synchronizace více obvodů AD9958 |

- |

|

3 |

MASTER_RESET |

I |

Reset |

PIC I/O |

|

4 |

PWR_DWN_CTL |

I |

Externí vypnutí |

GND |

|

5, 7, 11, 15, 19, 21, 26, 29, |

AVDD |

I |

Napájecí napětí analogové části (1,8V) |

analog. +1,8V |

|

30, 31, 33, 35, 36, 37, 39 |

|

|

|

|

|

6, 10, 12, 16, 18, 20, 25 |

AGND |

I |

Zem analogové části |

GND |

|

45, 55 |

DVDD |

I |

Napájecí napětí digitální časti (1,8V) |

dig. +1,8V |

|

44, 56 |

DGND |

I |

Zem digitální části |

GND |

|

8 |

CH0_IOUT |

O |

Výstup DA převodníku |

1. výstup |

|

9 |

CH0_IOUT |

O |

Komplementární výstup DA převodníku |

1. výstup kompl. |

|

13 |

CH1_IOUT |

O |

Výstup DA převodníku |

2. výstup |

|

14 |

CH1_IOUT |

O |

Komplementární výstup DA převodníku |

2. výstup kompl. |

|

17 |

DAC_RSET |

I |

Referenční proud pro oba DA převodníky |

R 4,7 kΩ na GND |

|

22 |

REF_CLK |

I |

Komplementární vstup hodinového signálu |

C 100 nF na GND |

|

23 |

REF_CLK |

I |

Vstup hodinového signálu |

hodinový signál |

|

24 |

CLK_MODE_SEL |

I |

Řídící vstup nastavující typ oscilátoru |

GND |

|

27 |

LOOP_FILTER |

I |

Externí kompenzace PLL filtru |

C 680pF na GND |

|

28, 32, 34, 38 |

NC |

- |

Bez vnitřního zapojení |

- |

|

40, 41,42,43 |

P0, P1, P2, P3 |

I |

Datové vstupy |

dig.vstupy |

|

46 |

I/O_UPDATE |

I |

Přesun dat ze vstupů do vstupních registrů |

PIC I/O |

|

47 |

CS |

I |

Výběr z více obvodů na společné SPI sběrnici |

PIC I/O |

|

48 |

SCLK |

I |

Hodinový signál sériové komunikace |

PIC I/O |

|

49 |

DVDD_I/O |

I |

Napájecí napětí digitální části (3,3V) |

dig. 3,3V |

|

50 |

SDIO_0, |

I/O |

Datový port sériové komunikace |

PIC I/O |

|

51 52, 53 |

SDIO_1:3 |

I/O |

Digitální porty |

1: PIC I/O; 3:GND |

|

54 |

SYNC_CLK |

O |

Čtvrtinová frekvence hodinového signálu |

- |

Schéma části zapojení integrovaného obvodu AD9958 je zobrazeno na obr. 2.3. V levé části schématu je vidět generátor hodinové frekvence (viz dále). Rezistory R5 a R6 přizpůsobují logické úrovně pro komplementární vstup externího hodinového signálu AD9958, který je oddělen keramickým kondenzátorem C1. Druhý hodinový vstup je připojen přes keramický kondenzátor C2 na zem. Sériová kombinace kondenzátoru C3 a R7 slouží jako externí kompenzace vnitřního PLL filtru. Rezistor R9 nastavuje maximální proud D/A převodníků. Rezistory R101, R102, R201 a R202 zatěžují proudové výstupy D/A převodníků. Všechny ostatní rezistory uvedené v tomto schématu slouží pro přizpůsobení logických úrovní.

Obr. 2.3 : Schéma části zapojení integrovaného obvodu AD9958

2.5.1.2. Synchronizace více AD9958

V této aplikaci bude využíván pouze jeden integrovaný obvod AD9958, a proto nebude synchronizace využita. Z toho vyplývá připojení synchronizačního vstupu SYNC_IN na zem a ponechání synchronizačního výstupu SYNC_OUT bez elektrického zapojení.

www.elweb.cz

2.5.1.3. Zapínání, reset

Integrovaný obvod AD9958 bude po zapnutí přístroje stále v zapnutém režimu. Vzhledem k napájení přístroje ze síťového adaptéru není nutné zabývat se příliš minimalizací proudového odběru. Z toho vyplývá připojení řídícího vstupu PWR_DWN_CTL na zem. Vstup MASTER_RESET je připojen na výstup mikrokontroléru a umožňuje tak programově restartovat DDS. Tím se nastaví veškeré vnitřní registry na výchozí hodnoty.

2.5.1.4. Hodinový signál

www.elweb.cz

Vzhledem k principu regulace výstupní frekvence v obvodu přímé digitální syntézy, ulehčí návrh volba frekvence hodinového signálu jako celá mocnina dvou (Hz). To umožní snazší řízení a zjednodušení programu mikrokontroléru. Výstupní frekvence v Hz pak bude přímo odpovídat binárnímu číslu určeného částí frekvenčního registru. Klasické krystaly se s takovouto hodnotou frekvence bohužel běžně nevyrábějí. Z tohoto důvodu jsem jako zdroj hodinové frekvence použil programovatelný krystalový oscilátor firmy Epson, konkrétně typ SG8002.

Oscilátory řady SG8002 obsahují krystal, programovatelnou děličku kmitočtu, fázový závěs PLL a paměť PROM. Současně je integrován programovatelý výstupní obvod, který umožňuje zatížit výstup obvody CMOS nebo TTL.

Parametry SG8002JC:

-napájecí napětí: 2,7 ÷ 5 V

-frekvenční stabilita ± 50 ppm

Frekvence hodinového signálu by měla být s rezervou vyšší než dvojnásobek maximální nastavitelné výstupní frekvence. Čím větší bude tato rezerva, respektive čím bude větší frekvenční odstup výstupní frekvence od nežádoucích obrazů ve výstupním frekvenčním spektru, tím budou kladeny menší nároky na strmost a tedy i složitost výstupního filtru.

Integrovaný obvod AD9958 dokáže pracovat s maximální hodinovou frekvencí 500 MHz. Obsahuje rovněž programovatelnou násobičku vstupní hodinové frekvence. Násobičku lze nastavit tak, aby násobila vstupní frekvenci celým číslem v rozsahu 4 ÷ 20. S ohledem na výše uvedené požadavky a možnosti jsem se rozhodl pro použití programovatelného oscilátoru SG8002 s naprogramovanou výstupní frekvencí 224 Hz, tedy 16 777 216 Hz a nastavení násobičky na 23, tedy 8-krát.

Výsledná vnitřní hodinová frekvence obvodu AD9958 bude pak:

|

|

(2.1) |

Maximální výstupní frekvence je teoreticky dle vztahu (1.4):

|

|

(2.2) |

|

|

|

Vzhledem k omezené strmosti výstupního rekonstrukčního filtru bude maximální výstupní frekvence nižší, konkrétně 40 MHz.

Nejmenší možný ladící krok (nejmenší možná změna) výstupní frekvence AD9958 je:

|

|

(2.3) |

|

Krok nastavení výstupní frekvence generátoru bude 1 Hz. Posledních pět bitů vkládaných mikrokontrolérem do delta registru bude tedy vždy nevyužito (budou zde vždy nuly). |

|

2.5.1.5. Výstupy

Oba kanály integrovaného obvodu AD9958 mají komplementární proudový výstup D/A převodníků. Dle katalogového listu mají být tyto proudové výstupy (na rozdíl od většiny ostatních DDS obvodů) zakončeny přes primární vinutí VF transformátoru nebo přes rezistory do napájecího napětí analogové části (+1,8 V). Vzhledem k požadované regulaci výstupní frekvence v rozsahu mnoha řádů by nebylo použití VF transformátoru vhodné. Z tohoto důvodu jsem zvolil variantu zakončení proudových výstupů rezistory. Při určení jejich hodnoty jsem vycházel z následujících informací uvedených v katalogovém listu.

-Maximální proud z jednoho výstupu je limitován hodnotou 15 mA.

-Při výstupním proudu 15 mA však dochází k nežádoucímu zkreslení a je vhodné nepřesahovat hodnotu 10 mA.

-Napětí na výstupech se může pohybovat maximálně v intervalu < UAVDD – UOUT_MAX ; UAVDD + UOUT_MAX >, kde UOUT_MAX= 0,5 V. (Zde je vhodné dodržet rezervu například 20 %.)

-Maximální rozsah výstupního proudu lze nastavit volbou hodnoty rezistoru RSET .

Výstupní proud jsem zvolil:

|

|

(2.4) |

Dle vzorce z katalogového listu pak:

|

|

(2.5) |

Po zaokrouhlení na nejbližší hodnotu v řadě E12:

|

|

(2.6) |

Výpočet hodnot zakončovacích rezistorů RTRM :

|

|

(2.7) |

Maximální amplituda na výstupech AD9958 bude tedy UmmAD = 0,8 ∙ 0,5 = 0,4 V.

2.5.1.6. Komunikace s mikrokontrolérem

Mikrokontrolér řídí obvod přímé digitální syntézy prostřednictvím 4-vodičové sériové sběrnice. Pin SCLK nese hodinový signál sériové komunikace, který je generován řídícím mikrokontrolérem. Pin SDIO_0 je využit pro vlastní sériová data. Po přenosu sériových dat (instrukcí a/nebo hodnot) do AD9958 je vyslán potvrzovací impulz. K tomu slouží pin IO_UPDATE. Díky tomuto potvrzovacímu impulzu jsou vnitřní registry v AD9958 změněny ve stejný okamžik a nepřepisují se v průběhu přenosu. Pin CS slouží k zahájení a ukončení přenosu. Rovněž by umožňoval výběr jednoho z AD9958, pokud by jich bylo na sériové sběrnici připojeno více.

Dále jsou k mikrokontroléru připojeny vstupy MASTER_RESET a SDIO_1. Pinem SDIO_1 jsou ovládány funkce související s lineárním rozmítáním. (Lineární rozmítání přesahuje rozsah této práce, ale je počítáno s jeho možnou budoucí programovou implementací.)

2.5.1.7. Přizpůsobení logických úrovní

Použitý mikrokontrolér PIC16F877 a rovněž i programovatelný oscilátor SG8002JC jsou napájeny napájecím napětím o hodnotě 5 V a jejich výstupní logické úrovně odpovídají logickým úrovním obvodů TTL. Při logické jedničce mají na výstupu tedy téměř 5 V. Digitální část obvodu AD9958 je však napájena napětím 3,3 V. Proto je potřeba logické úrovně přizpůsobit. Vzhledem k jednostranné komunikaci jsem použil pro toto přizpůsobení odporové děliče napětí – viz obr. 2.4. Případná obousměrná komunikace by byla také možná, protože pro zajištění logické jedničky na vstupu mikrokontroléru stačí napětí o hodnotě 2,4 V.

Obr. 2.4 : Přizpůsobení logických úrovní odporovým děličem napětí

Hodnoty odporů jednotlivých rezistorů odporového děliče napětí by neměly být příliš nízké, aby nedocházelo k proudovému přetížení výstupů mikrokontroléru (případně AD9958). Rovněž nesmí být příliš vysoké, protože komunikace probíhá na relativně vysokých frekvencích. Rozumným kompromisem jsou hodnoty v řádech stovek Ω až jednotek kΩ.

Hodnotu odporu rezistoru R1 jsem zvolil: R1 = 1,2 kΩ.

Hodnotu odporu rezistoru R2 jsem pak spočetl následovně:

|

|

(2.8) |

Z toho pak:

|

|

(2.9) |

Z řady E24 jsem pak vybral hodnotu R2 = 2,2 kΩ.

2.5.2. Diferenciální a výstupní zesilovače

Vzhledem k tomu, že jsou výstupy proudové a mají ústit do napájecího napětí +1,8 V, lze na nich pouze sledovat napětí, ale nelze je proudově dále příliš zatížit. Z výstupů je potřeba také oddělit stejnosměrnou složku. Oba tyto požadavky splňuje zapojení diferenciálního zesilovače s operačním zesilovačem. Schéma diferenciálního zesilovače je uvedeno na obr. 2.5.

Obr. 2.5 : Diferenciální zesilovač

Neinvertující vstupy diferenciálních zesilovačů označené jako UIN+ budou připojeny k výstupům AD9958 a invertující vstupy označené jako UIN- budou připojeny ke komplementárním výstupům AD9958. Pro stejné zesílení signálů na neinvertujícím i invertujícím vstupu budou mít rezistory R103 a R104 shodnou hodnotu odporu (R103 = R104). To samé platí i pro odpory dvojice rezistorů R105 = R106.

Zesílení A1 diferenciálního zesilovače je dáno poměrem odporů rezistorů R106/R104, respektive R105/R103 dle následujícího vztahu:

|

|

(2.10) |

Výchozí odpor rezistoru R103, respektive R104 by měl být dostatečně velký, aby nebyly proudové výstupy AD9958 příliš zatíženy, ale zároveň dostatečně malý, aby se příliš neprojevily parazitní kapacity, které by při výstupních frekvencích v řádech desítek MHz mohly způsobit nechtěný útlum signálu. Jako kompromis jsem zvolil hodnotu R103 = R104 = 1,2 kΩ.

Celkové zesílení diferenciálních a výstupních zesilovačů by mělo být takové, aby byla maximální amplituda výstupních signálů UmmOUT rovna 2,55 V při zátěži 50 Ω, respektive 10,2 V špička-špička bez zátěže.

Jak již bylo uvedeno výše, maximální amplituda na výstupech AD9958 UmmAD bude 0,4 V. Celkové zesílení bude tedy:

|

|

(2.11) |

Na poměru zesílení diferencíálních zesilovačů A1 a výstupních zesilovačů A2 by v ideálním případě nezáleželo, ale reálné operační zesilovače mají různé vlastnosti při různém výsledném zesílení. Z tohoto důvodu by měla být zesílení A1 a A2přibližně stejná. Použité operační zesilovače (viz dále) mají nejlepší vlastnosti přibližně v rozsahu výsledných zesílení 2 ÷ 3. Pro přesně stejná zesílení (A1 = A2) platí:

|

|

(2.12) |

Z toho pak:

|

|

(2.13) |

Nejbližší hodnota v běžně dostupné řadě E24 je 3 kΩ.

2.5.2.1. Výstupní zesilovače

Výstupní zesilovače slouží k napěťovému i proudovému zesílení výstupního signálu za výstupními LC filtry. Jedná se o operační zesilovače v neinvertujícím zapojení. Jeden z těchto zesilovačů je uveden na obr. 2.6. Zesílení výstupních zesilovačů je dle rovnice (2.12) A2 = 2,525. Odpor rezistoru R109 jsem zvolil: R109 = 1,2 kΩ. Z toho pak:

|

|

(2.14) |

Nejbližší hodnota v řadě je: R110 = 1,8 kΩ.

Rezistor R108 slouží jako symetrické zakončení výstupního LC filtru (viz dále) R108 = 50 Ω.

Rezistor R111 přizpůsobuje výstup na 50 Ω. R111 = 50 Ω.

Obr. 2.6 : Výstupní zesilovač

Maximální nastavitelná výstupní frekvence se bude pohybovat v řádech desítek MHz, výstupní amplituda v řádech jednotek voltů a výstupní proudy při impedančním přizpůsobení na 50 Ω budou dosahovat hodnot desítek mA. Z těchto důvodů je nutné volit speciální operační zesilovače. Svými parametry vyhovují například operační zesilovače určené pro xDSL technologie. Z nepříliš velikého výběru takovýchto operačních zesilovačů jsem dle parametrických tabulek a katalogových listů vybral integrovaný obvod THS3091 od Texas Instruments.

2.5.2.2. Vlastnosti THS3091

Vlastnosti obvodu THS3091 jsou převzaty z katalogového listu (3).

-Nízké zkreslení

- druhá harmonická složka – 66 dBc (při 10 MHz a zátěži 100 Ω)

- třetí harmonická složka – 74 dBc (při 10 MHz a zátěži 100 Ω)

-Nízký šum

- neinvertující proudový šum: 14 pA.Hz-1/2

- invertující proudový šum: 17 pA.Hz-1/2

- napěťový šum: 2 nV.Hz-1/2

-Šířka pásma 210 MHz (při zesílení A = 2 a zátěži RL = 100 Ω)

-Rychlost přeběhu 7300 V.µs-1

-Rozsah napájecího napětí ±5 V ÷ ±15 V

2.5.3. Výstupní filtry

2.5.3.1. Aktivní nebo pasivní ?

Nejprve jsem zvažoval použití aktivních filtrů. Respektive jsem hledal důvod, proč by aktivní filtry nebylo možné použít, a proč se ve spojení s přímou digitální syntézou ani běžně nepoužívají. Odpověď na tuto otázku je například v (4). Zde je uváděna dosavadní praktická hranice mezní frekvence ARC filtru přibližně 50 MHz. Píše se zde však také, že při mezních kmitočtech nad 1 MHz vznikají značné problémy s projevy reálných vlastností použitých součástek. Tyto problémy prý nastávají i při použití moderních operačních zesilovačů s tranzitními kmitočty v řádu stovek MHz. Mezní kmitočet zde použitého filtru by měl být 40 MHz. Proto bude vhodnější volit pasivní LC filtry.

2.5.3.2. Požadavky

Výstupní filtry slouží pro filtraci nežádoucích harmonických složek ve výsledném výstupním signálu obvodu přímé digitální syntézy. Při nastavení výstupní frekvence na maximální hodnotu fout = 40 MHz se ve frekvenčním spektru výstupního signálu objeví nejbližší obraz (nežádoucí harmonická složka) na frekvenci:

|

|

(2.15) |

Filtry musejí mít především dostatečnou strmost, aby dostatečně potlačily tento nežádoucí obraz. Vzhledem k parametrům ostatních součástek (především operačních zesilovačů a obvodu přímé digitální syntézy) lze považovat za minimální dostatečný útlum hodnotu 60 dB. V propustném pásmu by mělo být v ideálním případě nulové zvlnění přenosové funkce, respektive nulový útlum. Pro návrh filtru jsem zvolil maximální útlum v propustném pásmu 0,1 dB.

Generátor bude mít dva výstupy s nastavitelným vzájemným fázovým posuvem. V ideálním případě by filtry tedy měly mít nulový fázový posuv. To je v praxi samozřejmě nemožné. Zde však záleží jen na relativním fázovém posuvu mezi dvěma výstupními signály, nikoli na absolutním. Bude tedy stačit, když budou mít oba filtry stejný průběh fázového posuvu v závislosti na frekvenci. To je ovšem také prakticky nemožné kvůli rozptylu hodnot použitých součástek, respektive jejich toleranci.

Typ filtrů jsem vybíral s ohledem na jejich složitost při splnění požadované strmosti dané výše uvedenými požadavky a s ohledem na jejich citlivost změny fázového posuvu při změně hodnot použitých součástek. V aplikačních poznámkách firmy Analog Devices (5) doporučují použití filtru typu Cauer.

Pro návrh filtrů jsem použil návrhový systém Syntfil (6), ve kterém jsem rovněž provedl jednoduchou toleranční analýzu. Dále jsem postupoval dle (4) a (7).

2.5.3.3. Toleranční schéma

Toleranční schéma dolní propusti vychází z výše uvedených požadavků a je zobrazeno na obr. 2.7.

Obr. 2.7 : Toleranční schéma výstupních filtrů

Filtr by bylo možné realizovat různými aproximacemi. Následující tab. 2.3 uvádí jejich seznam včetně výsledného stupně filtru a nové hodnoty as. Tato tabulka vychází z tabulky generované internetovou aplikací Syntfil (6).

Tab. 2.3 : Srovnání aproximací

|

aproximace |

stupeň |

nová hodnota as (dB) |

|

Butterworth |

11 |

65.5 |

|

Chebyshev |

7 |

68.9 |

|

Inverzní Chebyshev A |

7 |

68.9 |

|

Cauer A |

5 |

66.9 |

Vzhledem k velikému rozdílu v řádech filtrů jsem se nakonec rozhodl pro použití aproximace Cauer A. Výsledné zapojení bude podstatně jednodušší než například v případě aproximace Butterworth a tím bude i méně náchylné na rozptyl hodnot použitých součástek.

Diferenciální zesilovač přizpůsobuje impedanci na 50 Ω. Výstupní filtry budou tedy rovněž přizpůsobeny na této impedanci se symetrickým zakončením.

V aplikačních poznámkách firmy Analog Devices (5) jsou uvedeny praktické testy několika typů filtrů s různým fyzickým rozmístěním jednotlivých součástek. Z těchto testů vyplývá, že je výhodné rozdělit každý kondenzátor, který je připojen k zemi, na kombinaci dvou paralelně zapojených kondenzátorů s poloviční hodnotou kapacity. Kondenzátory takovéto dvojce pak budou umístěny „proti sobě“.

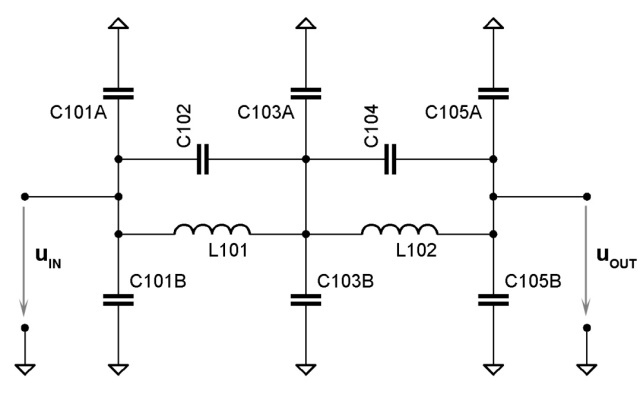

Výsledné schéma výstupního filtru je na obr. 2.8. Značení součástek obvodů připojených k prvnímu výstupu AD9958 pro přehlednost začíná číslem 101, k druhému pak 201.

Obr. 2.8 : Výstupní filtr

Hodnoty součástek byly vypočteny opět internetovou aplikací Syntfil (6) a jsou uvedeny v

Tab. 2.4 2.4. V této tabulce je rovněž uvedena použitá hodnota, respektive nejbližší hodnota v řadě nebo paralelní kombinace dvou kondenzátorů.

Tab. 2.4 : Hodnoty součástek použitých ve výstupních filtrech

|

součástka |

vypočtená hodnota |

použitá nominální hodnota |

|

C101 |

88.5 pF |

2x 47 pF |

|

C102 |

4.94 pF |

4,7 pF |

|

C103 |

152 pF |

2x 75 pF |

|

C104 |

9,19 pF |

8,2 pF |

|

C105 |

144 pF |

2x 75 pF |

|

L101 |

264 nH |

270 nH |

|

L102 |

272 nH |

270 nH |